03. Memory

时序逻辑

时钟(Clock)基于振荡器在低电平-高电平之间交替变化,提供连续的交变信号序列。两个相邻的上升沿之间的时间间隔称为一个周期(Cycle),周期的倒数即为频率(Frequency)。

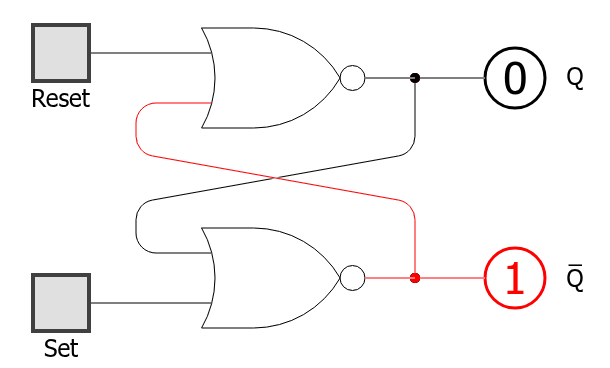

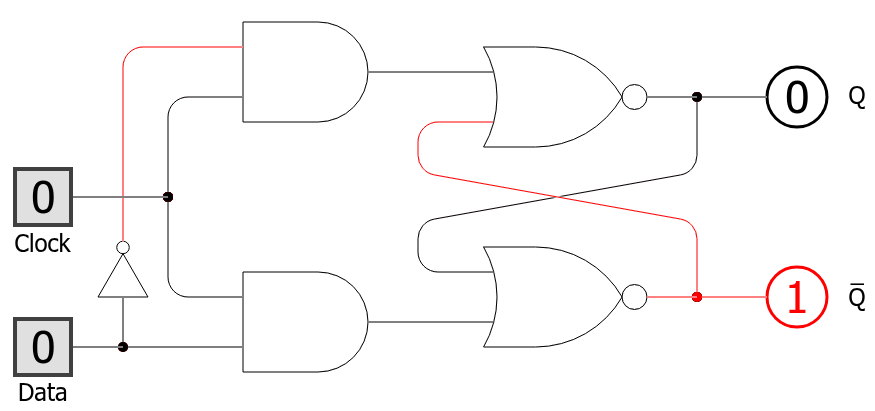

触发器(Flip-Flops)计算机中最基本的时序单元。

寄存器(Registers)具有记忆功能的设备,能够存储某一时刻的值。基本设计参数是宽度(Width)即它能够存储的比特位数,比如 16,32 或 64 位。此类寄存器的多位容量通常用字(Word)来表示。

内存(Memories)可以通过将很多寄存器堆叠起来形成随机存取内存(Random Access Memory,RAM)。每个寄存器都有一个地址(Address),可以通过地址访问特定的寄存器。基本设计参数是它的数据宽度(即每个字的宽度)和它的大小(RAM 中字的数量)。

Chip API

通过递归组合逐步构建内存块,一个 w-bit 的寄存器由 w 个 1-bit 寄存器构成,RAM8 内存块由 8 个 w-bit 寄存器构成,RAM64 内存块由 8 个 RAM8 内存块构成,以此类推。

芯片名: DFF

输入: int

输出: out

功能: out(t) = in(t-1)

说明: DFF 有现成的内置实现版本,无需自己实现。芯片名: Bit

输入: in, load

输出: out

功能: if load(t-1) then out(t) = in(t-1)

else out(t) = out(t-1)芯片名: Register

输入: in[16], load

输出: out[16]

功能: if load(t-1) then out(t) = in(t-1)

else out(t) = out(t-1)芯片名: RAMn // n 和 k 在以下有说明

输入: in[16], load, address[k]

输出: out[16]

功能: out(t) = RAM[address(t)](t)

用于 Hack 平台的具体 RAM 芯片如下:

芯片名 n k

RAM8 8 3

RAM64 64 6

RAM512 512 9

RAM4K 4096 12

RAM16K 16384 14芯片名: PC // 16-bit 的计数器

输入: in[16], load, inc, reset

输出: out[16]

功能: if reset(t-1) then out(t) = 0

else if load(t-1) then out(t) = in(t-1)

else if inc(t-1) then out(t) = out(t-1) + 1

else out(t) = out(t-1)触发器

https://www.codehiddenlanguage.com/Chapter17

Project 03

The computer's main memory, also called Random Access Memory, or RAM, is an addressable sequence of registers, each designed to hold an n-bit value. In this project you will gradually build a RAM unit. This involves two main issues: (i) using gate logic to store bits persistently, over time, and (ii) using gate logic to locate ("address") the memory register on which we wish to operate.

Objective

Build the following chips:

DFF (given)

Bit

Register

RAM8

RAM64

RAM512

RAM4K

RAM16K

PCIn principle, the DFF logic can be realized using Nand gates. However, we consider DFF primitive, and thus there is no need to implement it.

Implementation Tips

All the Implementation Tips of project 1 apply to this project also, so read them now.

There is only one modification: When implementing the chips of project 3, you can use, as chip-parts, any of the chips listed in projects 1, 2, and 3.

If you are using the desktop simulator, you will notice that nand2tetris/projects/3 consists of two subfolders named a and b. These subfolders are needed for technical reasons. Leave the structure of nand2tetris/projects/3 as is, and don’t move files from one subfolder to another.